**SDC4569A**

#### **General Description**

SDC4569A is a highly integrated current mode PWM control IC optimized for high performance, low standby power and cost effective offline flyback converter applications in sub 60W range.

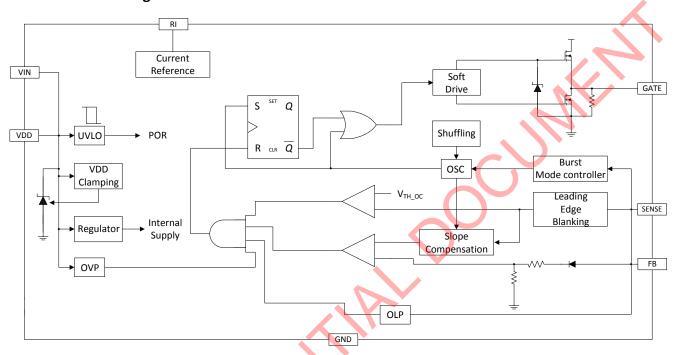

The internal slope compensation improves system large signal stability and reduces the possible subharmonic oscillation at high PWM duty cycle output. Leading-edge blanking on current sense(CS) input removes the signal glitch due to snubber circuit diode reverse recovery and thus greatly reduces the external component count and system cost in the design.

SDC4569A offers complete protection coverage with automatic self-recovery feature including cycle-by-cycle current limiting (OCP), over load protection (OLP), VDD over voltage clamp and under voltage lockout (UVLO). The gate drive output is clamped to maximum 12V to protect the power MOSFET.

#### **Features**

- Frequency shuffling technology for improved EMC performance

- Audio noise free operation

- Extended burst mode control for improved efficiency and minimum standby power design

- External programmable pwm switching

- Internal synchronized slope compensation

- Low VDD startup current and low operating current

- Leading edge blanking on current sense input

- Good protection coverage with auto self-recovery (UVLO/OVP/OCP/OLP)

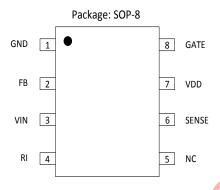

- Package: SOP-8

#### **Applications**

- Battery charger

- Power adaptor

- Set-top box power supplies

Figure 1. Package Type

**SDC4569A**

# **Pin Configuration**

Figure 2. Pin Configuration

| Pin No. | Pin Name | Function                                                                                                |  |  |  |

|---------|----------|---------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | GND      | Ground                                                                                                  |  |  |  |

| 2       | FB       | Feedback input pin. The PWM duty cycle is determined by voltage level into this pin and SENSE pin input |  |  |  |

| 3       | VIN      | Connected through a large value resistor to rectified line input for startup IC supply                  |  |  |  |

| 4       | RI       | Internal Oscillator frequency setting pin. A resistor connected between RI and GND the PWM frequency    |  |  |  |

| 5       | NC       | -                                                                                                       |  |  |  |

| 6       | SENSE    | Current sense input pin. Connected to MOSFET current sensing resistor node                              |  |  |  |

| 7       | VDD      | Chip DC power supply pin                                                                                |  |  |  |

| 8       | GATE     | Totem-pole gate drive output for the power MOSFET                                                       |  |  |  |

Table 1. Pin Description

**SDC4569A**

## **Functional Block Diagram**

Figure 3. Functional Block Diagram

SDC4569A

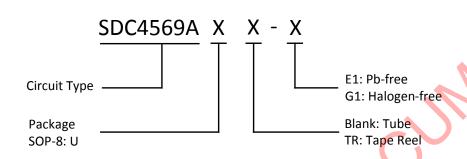

# **Ordering Information**

| Daakaaa | Temperature | Part N         | umber          | Marking ID |              | Packing   |  |

|---------|-------------|----------------|----------------|------------|--------------|-----------|--|

| Package | Range       | Pb-free        | Halogen-free   | Pb-free    | Halogen-free | Туре      |  |

| SOP-8   | -40℃~85℃    | SDC4569AUTR-E1 | SDC4569AUTR-G1 | 4569A      | 4569AG       | Tape Reel |  |

**SDC4569A**

**Absolute Maximum Ratings** (NOTE: Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device.)

| ,                                             |                    |         |      |

|-----------------------------------------------|--------------------|---------|------|

| Parameter                                     | Symbol             | Value   | Unit |

| VDD DC supply voltage                         | V <sub>DD</sub>    | -0.3~30 | V    |

| VDD clamp voltage                             | $V_{DD\_CLAMP}$    | 32      | V    |

| VDD DC clamp current                          | I <sub>CLAMP</sub> | 10      | mA   |

| V <sub>FB</sub> input voltage                 | V <sub>FB</sub>    | -0.3~7  | V    |

| SENSE input voltage                           | V <sub>SENSE</sub> | -0.3~7  | V    |

| V <sub>RI</sub> input voltage                 | $V_{RI}$           | -0.3~7  | V    |

| Operating junction temperature T <sub>J</sub> | T <sub>J</sub>     | 150     | °C   |

| Storage temperature T <sub>STG</sub>          | T <sub>STG</sub>   | -55~150 | °C   |

| Latch-up test per JEDEC 78                    | -                  | 200     | mA   |

| ESD,HBM model per Mil-Std-883H,Method 3015    | НВМ                | 2000    | V    |

| ESD,MM model per JEDEC EIA/JESD22-A115        | MM                 | 200     | V    |

Table 2. Absolute Maximum Ratings

# **Recommended Operating Conditions**

| Parameter                   | Symbol            | Min | Max | Unit |

|-----------------------------|-------------------|-----|-----|------|

| VDD DC supply voltage       | $V_{	ext{DD}}$    | 10  | 30  | V    |

| Operating Temperature Range | T <sub>OP</sub>   | -40 | 85  | °C   |

| Oscillation frequency       | ${ m f}_{ m osc}$ | 60  | 70  | kHz  |

Table 3. Recommended Operating Conditions

SDC4569A

# **Electrical Characteristics** (Ta=25°C, unless otherwise specified)

| Parameter                                         | Symbol                 | Condition                                                       | Min  | Тур  | Max  | Unit |

|---------------------------------------------------|------------------------|-----------------------------------------------------------------|------|------|------|------|

| Supply Voltage (VDD)                              |                        |                                                                 |      |      |      |      |

| VDD start up current                              | I <sub>STARTUP</sub>   | V <sub>DD</sub> =12.5V, RI=24k Measure Leakage current into VDD | -    | 3    | 20   | uA   |

| Operation current                                 | I <sub>DD</sub>        | V <sub>DD</sub> =16V, RI=24k,<br>V <sub>FB</sub> =3V            |      | 1.4  | -    | mA   |

| VDD under voltage lockout enter                   | V <sub>UVLO(ON)</sub>  | -                                                               | 6.5  | 7.5  | 8.5  | V    |

| VDD under voltage lockout exit (recovery)         | V <sub>UVLO(OFF)</sub> | - 13                                                            |      | 14   | 15   | V    |

| VDD zener clamp voltage                           | V <sub>DD_CLAMP</sub>  | I <sub>DD</sub> =10mA                                           | 30   | 32   | 34   | V    |

| Fe                                                | edback Inpu            | t Section(FB pin)                                               |      |      |      |      |

| FB open loop voltage                              | V <sub>FB_OPEN</sub>   | -                                                               | -    | 4.8  | -    | V    |

| FB pin short circuit current                      | I <sub>FB_SHORT</sub>  | Short FB pin to GND and Measure Current                         | -    | 0.8  | -    | mA   |

| Zero duty cycle FB threshold voltage zero         | V <sub>TH_OD</sub>     | V <sub>DD</sub> =16V, RI=24k                                    | -    | -    | 0.85 | V    |

| Power limiting FB threshold voltage               | V <sub>TH_PL</sub>     | -                                                               | -    | 3.7  | -    | V    |

| Power limiting debounce time                      | t <sub>D_PL</sub>      | -                                                               | -    | 35   | -    | ms   |

| Maximum duty cycle                                | DC <sub>MAX</sub>      | V <sub>DD</sub> =16V,RI=24k,<br>FB=3V,CS=0                      | 70   | 80   | 90   | %    |

| C                                                 | urrent Sense           | Input(Sense Pin)                                                |      |      |      |      |

| Leading edge blanking time                        | t <sub>BLANKING</sub>  | RI = 24K                                                        | -    | 300  | -    | ns   |

| Over current detection and control delay          | t <sub>D_OC</sub>      | V <sub>DD</sub> = 16V,<br>CS>V <sub>TH_OC</sub> , FB=3.3V       | -    | 75   | -    | ns   |

| Over current threshold voltage at zero duty cycle | V <sub>TH_OC</sub>     | FB=3.3V, RI=24k                                                 | 0.70 | 0.75 | 0.80 | V    |

| Oscillator                                        |                        |                                                                 |      |      |      |      |

| Normal oscillation frequency                      | f <sub>osc</sub>       | RI=24k                                                          | 60   | 65   | 70   | kHz  |

| Frequency temperature stability                   | $\Delta f_{TEMP}$      | V <sub>DD</sub> =16V,RI=24k,<br>Ta=-20°C~ 100°C                 | -    | 5    | -    | %    |

| Frequency voltage stability                       | $\Delta f_{VDD}$       | V <sub>DD</sub> =12V~25V,RI=24k                                 | -    | 5    | -    | %    |

**SDC4569A**

| Parameter                       | Symbol               | Condition                      | Min        | Тур | Max       | Unit |  |  |

|---------------------------------|----------------------|--------------------------------|------------|-----|-----------|------|--|--|

| RI open load voltage            | V <sub>RI_OPEN</sub> | -                              | -          | 2   | -         | >    |  |  |

| Burst mode base frequency       | f <sub>BM</sub>      | V <sub>DD</sub> = 16V, RI =24k | -          | 22  | <b>/-</b> | kHz  |  |  |

| Soft start time                 | t <sub>soft</sub>    |                                |            | 7   | -         | ms   |  |  |

|                                 | Gate Dri             | ve Output                      |            | 1   |           |      |  |  |

| Output low level                | V <sub>OL</sub>      | V <sub>DD</sub> =16V, lo=-20mA |            | )   | 0.8       | V    |  |  |

| Output high level               | V <sub>OH</sub>      | V <sub>DD</sub> =16V, Io=20mA  | 10         | -   | -         | V    |  |  |

| Output clamp voltage level      | $V_{CLAMP}$          | -                              | <b>)</b> - | 12  | -         | V    |  |  |

| Output rising time              | t <sub>r</sub>       | V <sub>DD</sub> =16V, CL=1nf   | -          | 125 | -         | ns   |  |  |

| Output falling time             | t <sub>f</sub>       | V <sub>DD</sub> =16V, CL=1nf   | -          | 50  | -         | ns   |  |  |

| Frequency Shuffling             |                      |                                |            |     |           |      |  |  |

| Shuffling frequency             | f <sub>osc</sub>     | RI=24k                         | -          | 64  | -         | Hz   |  |  |

| Modulation range/Base frequency | Δf <sub>OSC</sub>    | RI=24k                         | -3         | -   | 3         | %    |  |  |

Table 4. Electrical Characteristics

**SDC4569A**

#### **Function Description**

The SDC4569A is a highly integrated PWM controller IC optimized for offline flyback converter applications in sub 65W power range. The extended burst mode control greatly reduces the standby power consumption and helps the design easily meet the international power conservation requirements.

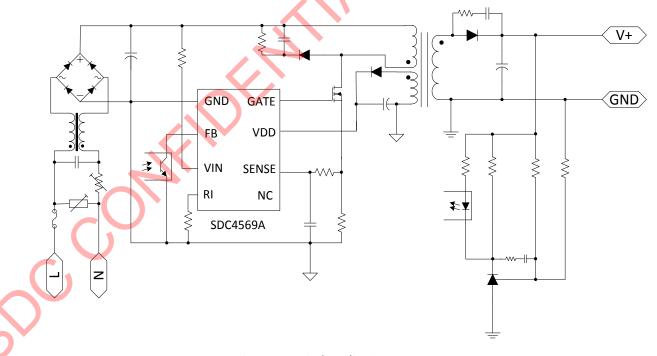

#### Startup Current and Start up Control

Startup current of SDC4569A is designed to be very low so that VDD could be charged up above UVLO threshold level and device starts up quickly. A large value startup resistor can therefore be used to minimize the power loss yet provides reliable startup in application.

#### **Operating Current**

The operating current of SDC4569A is low at 1.4mA. Good efficiency is achieved with SDC4569A low operating current together with extended burst mode control features.

#### Frequency shuffling for EMI improvement

The frequency shuffling/jittering (switching frequency modulation) is implemented in SDC4569A. The oscillation frequency is modulated with a random source so that the tone energy is spread out. The spread spectrum minimizes the conduction band EMI and therefore reduces system design challenge.

#### **Extended Burst Mode Operation**

Under zero load or light load condition, meet of the power dissipation in a switching mode power supply is from switching loss on the MOSFET transistor, the core loss of the transformer and the loss on the snubber circuit. The magnitude of power loss is in proportion to the number of switching events within a fixed period of time, Reducing switching frequent leads to the reduction on power loss and thus conserves the energy.

SDC4569A self adjusts the switching mode according to

the loading condition. Under no load to light/medium load condition, the FB input drops below burst mode threshold level, device enters burst mode control. The gate drive output switches only when VDD voltage drops below a preset level and FB input is active to output an on state, otherwise the gate drive remains at off state to minimize the switching loss and reduces the standby power consumption to the greatest extend. The frequency control also eliminates the audio noise at any loading conditions.

## **Oscillator Operation**

A resistor connected between RI and GND sets the constant current source to charge/discharge the internal cap and thus the PWM oscillator frequency is determined. The relationship between RI and switching frequency follows the below equation within the specified RI in  $k\Omega$  range at nominal loading operational condition.

$$fosc = \frac{1560}{RI(k\Omega)}(kHz)$$

## **Current Sensing and Leading Edge Blanking**

Cycle-by-cycle current limiting is offered in SDC4569A current mode PWM control. The switch current is detected by a sense resistor into the sense pin. An internal leading edge blanking circuit chops off the sense voltage spike at initial MOSFET on state due to Snubber diode reverse recovery so that the external RC filtering on sense input is no longer required. The current limit comparator is disabled and thus cannot turn off the external MOSFET during the blanking period. PWM duty cycle is determined by the current sense input voltage and the FB input voltage.

## **Internal Synchronized Slope Compensation**

Built-in slope compensation circuit adds voltage ramp onto the current sense input voltage for PWM generation.

**SDC4569A**

This greatly improves the close loop stability at CCM

and prevents the sub-harmonic oscillation and thus reduces the output ripple voltage.

#### **Gate Drive**

SDC4569A Gate is connected to an external MOSFET gate for power switch control. Too weak the gate drive strength results in higher conduction and switch loss of MOSFET while too strong gate drive output compromises the EMI. A good tradeoff is achieved through the built-in totem pole gate design with right output strength and dead time

control. The low idle loss and good EMI system design is easier to achieve with this dedicated control scheme. An internal 12V clamp is added for MOSFET gate protection at higher than expected VDD input.

#### **Protection Controls**

Good power supply system reliability is achieved with its rich protection features including cycle-by-cycle current limiting (OCP), over load protection (OLP) and over voltage clamp, under voltage lockout on VDD (UVLO).

## **Typical Application**

Figure 4. Typical Application

SDC4569A

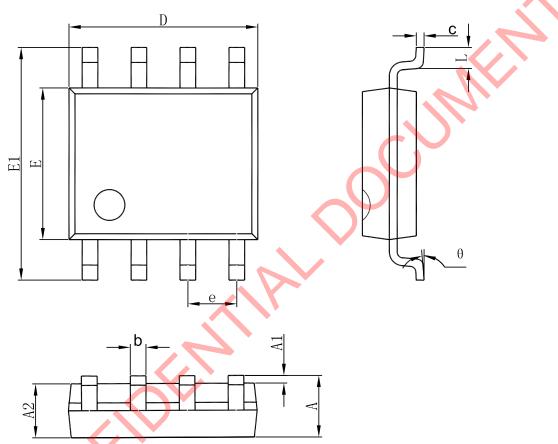

# Package Dimension SOP-8

| Symbol | Dimensions I | n Millimeters | Dimension | s In Inches |

|--------|--------------|---------------|-----------|-------------|

| Symbol | Min          | Max           | Min       | Max         |

| A      | 1.350        | 1.750         | 0.053     | 0.069       |

| A1     | 0.100        | 0.250         | 0.004     | 0.010       |

| A2     | 1.350        | 1.550         | 0.053     | 0.061       |

| b      | 0.330        | 0.510         | 0.013     | 0.020       |

| С      | 0.170        | 0.250         | 0.007     | 0.010       |

| D      | 4.700        | 5.100         | 0.185     | 0.201       |

| e      | 1.270        | 1.270(BSC)    |           | (BSC)       |

| E      | 5.800        | 6.200         | 0.228     | 0.244       |

| E1     | 3.800        | 4.000         | 0.150     | 0.157       |

| L      | 0.400        | 1.270         | 0.016     | 0.050       |

| θ      | 0°           | 8°            | 0°        | 8°          |

**SDC4569A**

# Shaoxing Devechip Microelectronics Co., Ltd.

http://www.sdc-semi.com/

#### **IMPORTANT NOTICE**

Information in this document is provided solely in connection with Shaoxing Devechip Microelectronics Co., Ltd. (abbr. SDC) products. SDC reserves the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at anytime, without notice. SDC does not assume any responsibility for use of any its products for any particular purpose, nor does SDC assume any liability arising out of the application or use of any its products or circuits. SDC does not convey any license under its patent rights or other rights nor the rights of others.

© 2013 Devechip Microelectronics - All rights reserved

Contact us:

Headquarters of Shaoxing Shenzhen Branch

Address: Tian Mu Road, No13, Address: 22A, Shangbu building, Nan Yuan Road, No.68,

Shaoxing city, Zhejiang province, China Futian District, Shenzhen city, Guangdong province, China

Zip code: 312000 Zip code: 518031

Tel: (86) 0575-8861 6750 Tel: (86) 0755-8366 1155

Fax: (86) 0575-8862 2882 Fax: (86) 0755-8301 8528